摘 要:为了验证遥测系统中被测对象的功能可靠性,研制了一种基于pci总线的数字量测试台,它用来模拟输出各种测试信号。数字量测试台的实现以fpga为核心,分别实现了模拟测试信号源的输出和与pci总线的通信。功能仿真和实际测量验证了设计的可行性。

关键词:fpga;pci;遥测系统

遥测技术是指对被测对象的某些参数进行远距离测量,并传送到接受点的一种测量技术。遥测系统在大型核心飞行试验中是不可缺少的重要组成部分,遥测系统用于获取飞行试验中被测系统的工作状态参数和环境数据,为确定被测系统的性能或进行故障分析提供依据。数字量变换器作为遥测系统被测系统的核心,它的主要功能是控制接收被测系统各种飞行参数。数字量变换器的可靠性是影响遥测结果的核心环节,其精度关系到被测系统研制和实验过程中的实验数据可信度,其性能关系到实验的成败。如何准确、客观、高效地评价数字量遥测变换器的性能,是数字量变换器生产中的重要环节。

课题所研制的数字量变换器测试台用于数字量变换器的单机测试,可以广泛应用于被测系统研制、生产过程中数字量变换器的测试与控制。本测试装置属于自动测试系统(ats)的范畴,它的使用,将改变数字量遥测变换器传统的手工测试方法,使其生产、应用中的测试实现自动化,必将提高数字量遥测变换器的生产水平和质量,增进遥测系统的联试水平,降低生产和试验成本。

1 系统的整体硬件电路设计

数字量测试台实现的模拟测试信号包括激光惯组脉冲、勤务信号、计算机字。LOCAlHOst数字量变换器测试台要实现课题任务中的所有功能,必须产生各个功能模块的控制信号,这个系统具有复杂的时序,设计中选用fpga作为逻辑控制器就得到了很好的效果,同时fpga的可编程逻辑特性能够简化硬件电路设计,提高系统的可靠性与稳定性。

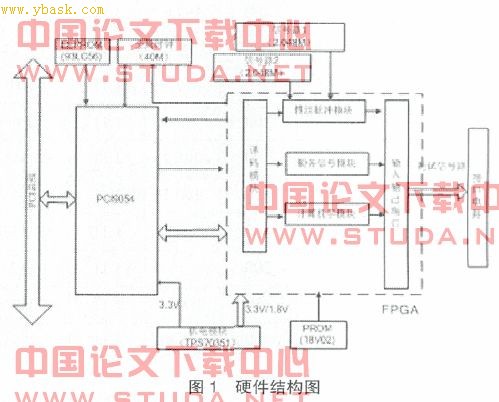

fpga具有小批量,低投入,高性能,高密度,开发周期短等诸多优点,使国内更多的工程师们乐于采用。由于不需要任何投片费用,也不需要建立任何生产线,因此,采用fpga所需的投资远远低于asic的投资。据估计,引进一套先进的fpga自顶向下设计工具所需费用还不到asic所需的1/10,而大力推广先进的fpga设计方法,既可以降低诸多产业投资成本,也可培养自顶向下的设计人才,从而为将来国内asic产业的快速、健康发展打下坚实的基础[1][2]。硬件结构见图1。

1.1 核心控制部分

fpga采用xilinx公司的xc2s200e,xc2s200e是低电压(3.3 v和1.8 v)供电,含有5 292个逻辑单元,高达150 000个门电路,它内部有丰富的门阵列资源,56 kbits的ram缓冲器,通过在fpga中编写硬件逻辑,来实现数字量指令的发送和信号。除此之外,数字量变换器测试台系统中,fpga的另一功能是实现pci总线和本地总线的通信功能。

1.2 数字量测试台的的通信方式

上位机与硬件电路的通信采用pci总线的通信方式。pci的含义为周边设备互连(peripheral computer interconnect),是一种高带宽、即插即用(pnp)的总线协议,它被用来满足当今高性能pc机和工作站以及它们的高带宽应用。pci数字卡中接口芯片选用的是plx公司的pci9054这一款芯片。该芯片是32位、33 mhz的通用pci总线控制器专用芯片。它符合pci总线规范2.2版,突发传输速率达到132 mb/s。pci9054内部有6个可编程的fifo,以实现零等待突发传输及局部总线和总线之间的异步操作。

本课题选用pci9054的工作方式为c模式,数据传输模式为pci target(pci从模式)。

2 fpga内部系统各功能模块的实现

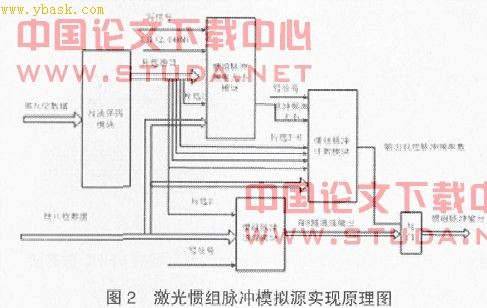

2.1 激光惯组脉冲信号

激光惯组脉冲信号输出为16路,分为单数路和偶数路,单数路和偶数路分别采用两个不同的信号源;脉冲信号的频率可以选定10 k~256 k,至少20分档,包括256 k这个频率;脉冲信号的个数可以按组发出,每组的个数可以预定,并不小于224。

。

。

片选译码模块:fpga和pci9054连接的数据总线宽度为16位,高8位数据作为各模块的片选译码信号,低8位数据作为模块中实现功能的有效数据。

频率大小模块:这个模块是实现惯组脉冲的频率范围选择,利用晶振源clk(2.048m)分频得到,定义惯组脉冲输出的频率大小为f(10 k≤f≤256 k),分频数为n,则8≤n=2.048 m/f≤204.8,上位机发送一个8位的二进制数(低8位数据),记为分频数,在写信号的边沿触发下写入模块寄存器中,换算成十进制数的范围为0~255,由上面换算可知可以实现10 k~256 k的任意分频,也就满足任务中10 k~256 k的20分档。但是,当分频数是小数时会存在微小误差,因此20分档频率尽可能取分频数是整数的脉冲通道模块:这个模块实现了惯组脉冲通道位的选择,低8位数据的每位控制一个通道,输出端与门相连,为‘1’时通道打开,为‘0’时通道关闭。

脉冲计数模块:这个模块主要实现对频率大小模块中输出的的脉冲频率进行计数。要求每路脉冲的个数不小于224,在设计中基数用32位,所以最多可以实现232个脉冲数。32位数据由低8位数据端分开4次输入脉冲计数模块中的32位寄存器,低位在前,高位在后,片选3-6为

[1] [2] 下一页