论文关键字:abc mv文件时序 综合

论文摘要:abc是一款时序逻辑电路的综合和验证的软件系统。abc为查找表和标准块整合了基于aigs(这个图只有与门和非门)的逻辑优化和基于技术映射的最优延迟dag(无回路有向图)。mv是一种为描述时序层次电路系统而设计的语言,它能以层次形式来描述电路系统。abc提供了对输入mv文件的支持,但其对mv文件的时序支持有限,本文讨论了其解决方案。

1 电路逻辑综合的一些常用方法

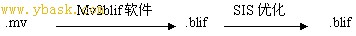

1.1 使用sis优化

输入.mv文件,经过mv2blif软件处理后,产生.blif文件,然后送入sis综合软件处理,生成优化后的blif文件,如下图所示:

shape \* mergeformat

图 1.1

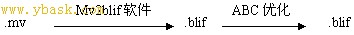

1.2 使用abc优化

输入.mv文件,经过mv2blif软件处理后,产生.blif文件,然后送入abc处理,生成优化后的blif文件,如下图所示:

shape \* mergeformat

图 1.2

1.3 对比两种方法

使用sis优化已经是比较陈旧的方法,现在更多的是使用abc进行优化。LOcAlhoST我们知道,数据结构和算法是一个软件能否成功应用的核心,sis在近几年一些最新的改变中没能提供一个良好的编程环境,比如对技术映射和延迟的整合。而且sis在处理大型电路显得力不从心,效率低下。而abc使用了一种更为简单的数据结构aigs(由两输入的与门和非门组成的多层逻辑网),使得电路综合和验证的质量和运行时间方面都得到很大改进。abc提供了时序和组合的综合算法,其现在版本在优化延迟和启发式的缩小电路面积方面已能优化包含100k门和10k时序元素的门级设计。

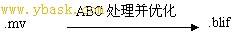

但abc本身就能输入.mv文件,我们能否省去mv2blif的步骤,让abc直接读入mv,从而也能减少错误,提高效率,因为再好的软件或多或少总会存在一些错误,少用一个软件意味着我们能减少更多的错误。所以下面就是我们想要得到的版本:

shape \* mergeformat

2 研究中发现问题及其原因

2.1 abc中采用的网络介绍

在读入特定电路设计文件经过软件处理,就形成当前的网络。abc通过一系列对当前网络的转换来处理这个电路设计类似于sis。abc中的网络有其特定类型,包括netlist,logic network和aig网络,下面简要介绍各个网络。

2.1.1 netlist网络

如果编程者在输入文件中加入一个新的类型,想成功通过解析就必须熟悉netlist网络的表示形式,因为解析一个输入文件,netlist网络是必然被创建的。netlist可以说是一个基本原始的网络表示形式,它与输入文件的设计一一对应,包含nets,logic nodes,latches和pi/po 端点。每个net有一个唯一的名字。nodes和latches是由它们所驱动的net来区分。每个nodes和latches只有一个输出。每个pi端点、node和latch驱动一个net。同样每个latch、po端点和功能结点(有一个或多个输入)由一个net驱动。一个net能驱动有仅只有一个latch、node或者po端点。例如,一个net不能同时驱动一个node和一个latch。在netlist中,net与net之间不能相连,非net结点与非net结点也不能相连,只能通过net相连。功能结点采用sops或者aigs来表示。

2.1.2 logic network网络

一个logic network实际上是一个netlist去掉nets后的网络,sis就是用logic network网络所表示。在abc,默认的表示是aig网络,但logic network是一种很有效的中间过渡网络表示形式。在logic network网络中只保留 了pi/po/latch/latch-input/latch-output这几种数据结构的名字,丢弃了内部node的名字。因为abc采用aig进行深层次的综合时,一些aig操作很难保存aig结点的名字,比如重写。在logic network中,nodes 能与另一个nodes直接相连。pi/po端点与node直接相连。一个po端点与一个pi端点如果有一样的名字和功能,能直接相连。一个pi端点可能有两个扇出但没有扇入。一个po端点只有一个输入但没有输出。端点并不是一个逻辑node也没有逻辑功能。指向端点的指针集合不能通过一个内部node的dfs遍历方法来获取。在logic network网络中,指向pi/po端点的指针集合储存在相应的数组。

2.1.3 aig网络

aig网络是abc中所采用网络的内部主要表示形式。aig是abc所特有的,其每个node是两输入的与门和一个扇入/扇出边,并且这个边有一个可选属性指示是否对该边进行取反。在构造aig的同时,aig能被压缩通过

[1] [2] [3] [4] 下一页